|

Project: vCPU |

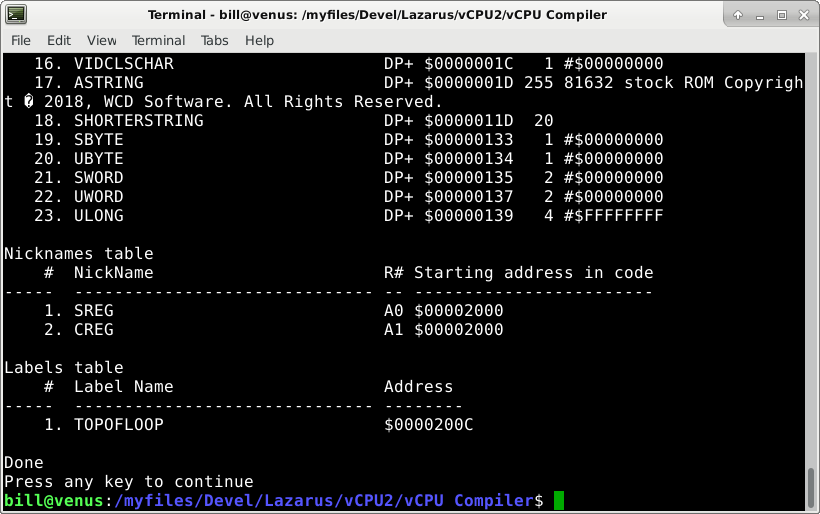

Presenting a virtualized CPU and computerThe 81632 virtualized chip is an 8/16/32-bit processor with a 24-bit address space. Eight 32-bit data registers, and eight 32-bit address registers, make data handling a breeze. Innovative features include eight flags in the processor status register, available for use, and coprocessor support to provide auxiliary services. A memory explorer allows direct access to seven 24-bit pages of memory (six RAM, one ROM). In addition, a jump table linked to unused instruction codes provides the opportunity to "code your own instructions." A mix of One- and two-byte instructions helps keep code size smaller. A mostly load/store architecture forces a RISC approach and simplifies the implementation of the instruction processor, with the side benefit of improving execution times. Program branching can be relative to the Program Counter, or absolute; likewise, data accesses can be absolute, or relative to the Data Segment Pointer. Address registers can be used for indirection on load/store, or for indexing addresses in several modesThe instruction set has been defined and mapped out, and the processor core, all registers, and the memory model have been implemented. The image above is of the latest version, processing NOPs. Work is now proceeding with an assembler (output pictured below), following which the instruction processor will be implemented. After that, some of the subsystems (video, keyboard, disk access, memory management) will be implmented; and a functional ROM will be coded. Better to do it this way, (assembler, then processor) than to have to hand-code tons of test stuff, and end up building the assembler anyway. Hand-coding from assembly language isn't hard; it's just tedious and generally involves lots of hexadecimal math (even I haven't got my hex multiplication tables down to memory, yet). This project is intended to be educational to both the programmer and the user. It will be publicly released, along with the development ROM, as open source software. Many months of thought have gone into this design (including lessons learned from an abortive first attempt, two years ago). Development is proceeding quickly enough.

|